# Diseño en VHDL de un transceptor de la interfaz de línea digital E1 y su implementación en un FPGA

Yudith Florencia Gonzalez Padilla<sup>1,2</sup>, Topacio Osuna Altamirano<sup>2</sup>, Josué López Leyva<sup>2</sup>.

<sup>1</sup>Instituto Superior Politécnico José Antonio Echeverría, Cujae, Calle 114 No. 11901. e/

Ciclovía y Rotonda. Marianao 15. La Habana, Cuba. CP 19390.

<sup>2</sup>Centro de Investigación Científica y de Educación Superior de Ensenada; Carretera Ensenada-Tijuana No. 3918, Zona Playitas, C.P. 22860, Ensenada, B. C. México.

pupi\_bonita@yahoo.es, tosuna@cicese.edu.mx, jalopez@cicese.edu.mx

*Paper received on 01/10/12, Accepted on 25/10/12.*

**Abstract.** Se presenta el diseño de un módulo de hardware embebido con las funcionalidades de una interfaz digital E1. El sistema diseñado realiza las tareas de un transmisor-receptor, encargándose de acciones como la codificación y decodificación del flujo digital, el análisis del sincronismo de la trama y la generación de relojes. También incorpora una interfaz con un microprocesador para la configuración de los parámetros iniciales del funcionamiento o selección de los modos de operación. Cada uno de los bloques presentes en el sistema se ha diseñado a través del lenguaje de descripción de hardware VHDL empleando el software Xilinx ISE Design Suite 10.1; e implementado en la tarjeta de desarrollo SPARTAN3 Starter Kit. La principal contribución del trabajo es un módulo de hardware reutilizable que aumenta el rendimiento, reduce la latencia de tratamiento de datos en comparación con soluciones de circuitos integrados existentes y tiene integrado un mecanismo de análisis de fallos en la transmisión.

**Keywords:** FPGA, Dispositivo programable, flujo E1, trama, multitrama.

## 1 Introducción

A inicios de la década de los noventa, las telecomunicaciones y las redes de datos incorporaron el uso de los FPGAs a sus aplicaciones, dado el tamaño y sofisticación de los mismos. Sin embargo, no es hasta principios del 2000 cuando se llegó a tener FPGAs de alto rendimiento con sistemas de millones de compuertas y bloques embebidos de microprocesadores, procesadores digitales de señales, e interfaces de entrada/salida de muy alta velocidad pudiendo sobrepasar los 5 Gbps. Lo anterior justifica que estos dispositivos sean aptos para casi cualquier aplicación, como por ejemplo sistemas de comunicaciones, procesamiento de imágenes y video, redes neuronales artificiales y procesamiento digital de señales, por mencionar algunos.

Los módulos de propiedad intelectual, también conocidos como IP CORE, son descripciones software de componentes hardware, que implementados en un dispositivo programable como un FPGA, pueden sustituir la circuitería instalada, con ventajas tales como: la reducción en los costos y la capacidad de reutilización.

En las comunicaciones digitales el estándar más empleado es la interfaz de línea digital de 2.048 Mbps, denominada E1, dentro de la jerarquía de dicha red. Esta tecnología se utiliza principalmente en pizarras telefónicas (PBX), centrales locales o en la trasmisión de datos a través de un enlace dedicado que puede ser desde 64 kbps hasta 2Mbps, y constituye el nivel primario para jerarquías de mayor encapsulado. Se describe en las recomendaciones UIT-T G.732, UIT-T G.703, UIT-T G.704, UIT-T G.706. En este trabajo se presenta el diseño e implementación de un módulo de propiedad intelectual capaz de sustituir el hardware de una interfaz de línea digital E1.

## **2 Especificaciones de las recomendaciones G.732, G.703, G.704 y G.706 de la UIT**

La trama de trasmisión E1 se conforma a través del multiplexado en tiempo de 32 canales de 8 bits cada uno. Cada trama dura 125μs y según los 256 bits que contiene se alcanza una velocidad de 2048kbps. De los 32 intervalos de tiempo, 30 son canales telefónicos de 64kbps y 2 de igual velocidad destinados a la señalización y sincronismo de trama. Según la información que viaja en el intervalo cero, se pueden distinguir dos tipos de tramas: las pares y las impares. Todas las tramas pares contienen la bandera de alineación, dada por la secuencia “X0011011” que permite la recuperación del sincronismo de 8 kHz en el receptor. Las tramas impares no llevan esta información en dicho canal, en cambio contienen bits de supervisión y alarma.[1]

Para aumentar las facilidades de gestión en la trama E1 de la RDSI (Red Digital de Servicios Integrados) de banda estrecha y para proporcionar a los usuarios canales transparentes con el fin de conservar la integridad de los bits, existe el concepto de multitrama. La multitrama consiste en una agrupación de 16 tramas E1, las cuales a su vez se divide en dos submultitramas (SMT) de 8 tramas, para computar los coeficientes de CRC-4 denominadas SMT I y SMT II. Dichos coeficientes se ubican en el primer bit de cada trama impar de la submultitrama que se envía detrás. Además, en la SMTII las últimas tramas en la misma posición proporcionan información sobre la existencia de errores en la transmisión de los canales de usuario.[2-3]

Un código de línea es usado en un sistema de comunicaciones como soporte para la transmisión. El estándar G703 especifica muchas opciones para la transmisión física, especificando de forma casi exclusiva el formato del código de línea HDB3. En HDB3 un ‘1’ se representa con polaridad alternada mientras que un ‘0’ toma el valor cero. Este tipo de señal no tiene componente continua ni de bajas frecuencias, pero presenta el inconveniente que cuando aparece una larga cadena de ceros se puede perder el sincronismo al no poder distinguir un bit de los adyacentes. Para evitar esta situación, el código establece que en las cadenas de cuatro ceros o más, se reemplace el cuarto ‘0’ por un bit denominado “bit de violación” el

cual tiene el valor de un ‘1’ lógico e igual polaridad que el ultimo ‘1’ y si hay cadenas continuas de cuatro ceros o cantidad de violaciones pares además del “bit de violación”, se le agregan primero un bit de balance que es un pulso con distinto signo que el anterior. [4]

### 3 Descripción del diseño del transceptor

El transceptor de flujo E1 quedó concebido para transportar en un sentido un flujo de datos desde su entrada serie de 2048 kbps (STBUSTX) hacia su salida a la línea E1, incorporándole en los canales correspondientes las banderas que requiere, así como la codificación necesaria para la transmisión.

En el otro sentido, el transceptor conduce la trama E1 adquirida hacia su salida serie de 2048 kbps (STBUSRX), a la cual llegará luego de ser decodificada y evaluada detalladamente. Ambos sentidos cuentan con el suministro de las fuentes de reloj necesarias para ejecutar sus funciones y además, se debe proporcionar una interfaz a la que se entregue toda la información requerida por el microprocesador.

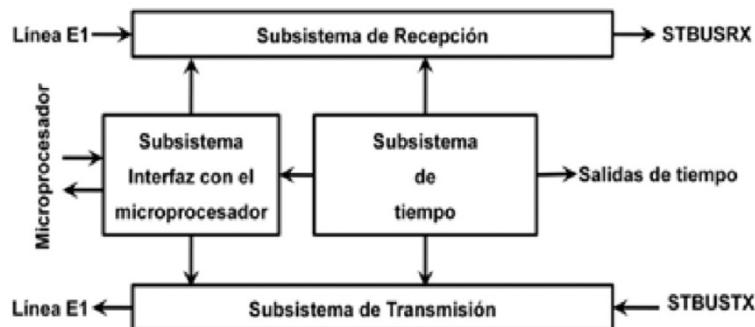

**Fig. 1.** Estructura del sistema transceptor de flujo E1.

En la figura1 se observa el esquema general del sistema y la relación existente entre los cuatro subsistemas que lo conforman. El subsistema de transmisión, transporta los datos entregados de forma serie por la entrada STBUSTX hacia la línea con la codificación HDB3 y las banderas que necesita la trama para ser transmitida. El subsistema de recepción, recibe los datos de la línea E1 codificados en HDB3 y los entrega por la salida STBUSRX como una cadena de bits decodificados en forma serie. El subsistema de reloj, obtiene las bases de tiempo necesarias en todos los bloques y las ofrece como salidas del transceptor, con el fin de lograr la sincronización con otros dispositivos. El subsistema de interfaz con el microprocesador, brinda la posibilidad de controlar y de verificar el funcionamiento del transceptor.

#### 3.1 Subsistema Trasmisor

En el trasmisor se selecciona la señal de sincronismo (FT sincronismo externo o FO sincronismo interno) y se pone en ‘1’ la señal que habilita el proceso de tras-

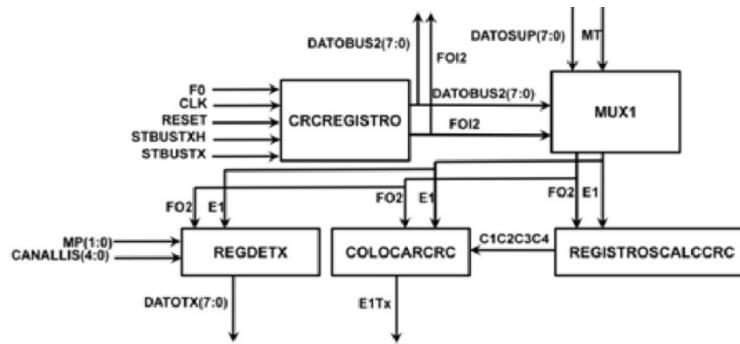

misión (STBUSTH). Así, se van tomando los bytes del STBUSTX y se les incorpora la bandera e información de señalización, los bytes conformados van saliendo por la señal DATOBUS2. A continuación se llenan los canales de la trama que sale por la señal E1, con los datos de la señal DATOBUS2 o del microprocesador (DATOSUP), según el modo de trabajo seleccionado. Por la señal E1 van saliendo las tramas a las cuales se les calcula los coeficientes CRC que serán colocados en la próxima submultitrama. Además, como salida tiene también a la señal DATOTX que entrega el canal que se le realiza la prueba en caso de que el sistema esté configurado en modo de prueba lazo interno selectivo. En la figura 2 se puede observar las señales descritas y los bloques que desempeñan estas funciones. Por último se le realiza la codificación HDB3 a los datos que salen por la señal E1Tx colocando los bits de violaciones y balance correspondientes. Finalmente la señal bipolar es puesta en la salida a través de dos señales SalirR1 y SalirR2.

**Fig. 2.** Estructura del bloque SISTEMACRC del Subsistema Trasmisor.

### 3.2 Subsistema Receptor

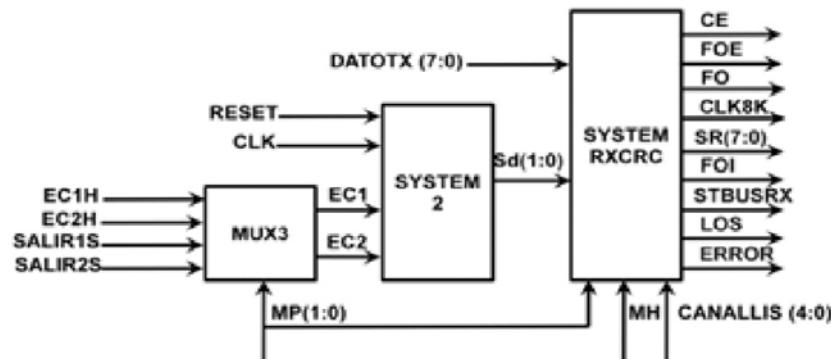

El flujo E1 que circula por la línea pasa primero por un acoplador que le entrega al sistema dos señales EC1H y EC2H que contienen los pulsos positivos y negativos respectivamente de la codificación HDB3. Según el modo que este configurando el microprocesador (normal o lazo de prueba) se toman las señales EC1H y EC2H o las provenientes del trasmisor SalirR1 y SalirR2. Así, de la entrada seleccionada se crea una señal (Sd) con los bits pertenecientes a la decodificación. Despues se realiza la búsqueda de la bandera de alineación de la trama bit a bit, mientras esto no suceda, el bloque de recepción no tomará ninguno de los datos que se reciban como parte del flujo E1. En caso de pérdidas de alineación, se activa una señal LOS a la salida y se inicializa todo los procesos del sistema. A continuación se realiza la comprobación de CRC y en caso de haber error se activa una señal ERROR a la salida, además los bits de indicación de error de la multitrama son colocados a la salida con la señal CE. Finalmente, la salida STBUSRX estará en tercer estado hasta que el microprocesador la active para poner los canales proveenientes de la línea o información del micro (DATOTX). En la figura 3 se muestran los bloques y señales involucradas en este subsistema.

**Fig. 3.** Diagrama en detalle del Subsistema de Recepción.

### 3.3 Subsistema Tiempo

Este subsistema ofrece una salida de reloj a una frecuencia de 4096 kHz de la que se deriva la fuente de reloj de 2048 kHz; además debe ser capaz de sincronizarse con la fuente de reloj que se seleccione. Se utilizó el bloque CDR, que constituye una aplicación que brinda el fabricante Xilinx para la recuperación del reloj de los datos recibidos y la generación de un reloj libre de valor especificado cuando no se introduzcan datos a la entrada.

### 3.4 Interfaz con Micróprocesador

La interfaz con el micróprocesador constituye un grupo de bloques formado por memorias RAM, donde se almacenan los datos entregados por el micróprocesador para la configuración del transceptor y los datos entregados por este (incluye los datos recibidos de la línea E1 y los datos a transmitir por ella), permitiendo el acceso a toda esta información por parte del micróprocesador.

El micróprocesador configura cada intervalo de tiempo del flujo de salida E1TX en dos modos de trabajo: modo transparente y modo mensaje. Esto se hace a través de dos memorias, una de 32x8 y otra de 32x9. La primera se llena con los datos a transmitir, que se entregan por STBUSTX, y la segunda con los datos de configuración que brinda el micróprocesador. Cada vez que se vaya a transmitir un canal, se analiza el bit 9 de la memoria de configuración ('0' modo transparente, '1' modo mensaje) y en función de esto se transmite el dato entregado por STBUSTX o el dato existente en los 8 bits restantes de la memoria configurada por el micróprocesador.

El micróprocesador indica también modos de prueba a través de una memoria de 1x7 donde los 2 bits más significativos indican el modo de trabajo a utilizar ('00' modo normal, '01' lazo interno completo, '10' lazo interno selectivo). En el lazo interno completo, la salida del bloque transmisor se conecta a la entrada del bloque receptor. En el lazo interno selectivo, se recibe de la línea una trama E1 a la que es incorporado un canal de la transmisión. Este canal es indicado con los 5 bits menos significativos de la memoria.

## 4 Comprobación del funcionamiento del transceptor

Se comprobaron los subsistema de manera individual, a través de simulaciones y mediciones capturadas luego de la descarga del software confeccionado en el FPGA Spartan3. Para la realización de las pruebas se utilizan algunas herramientas que permiten la verificación y validación del diseño.

### 4.1 Comprobación del trasmisor

Para el análisis del subsistema trasmisor se confecciono la tabla 1 que predice el resultado de la simulación. En ella aparece la entrada de datos STBUSTX y el resultado esperado.

**Table 1.** Entradas y salidas del boque de trasmisión.

|         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| STBUSTX | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| Salir2  | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| Salir1  | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

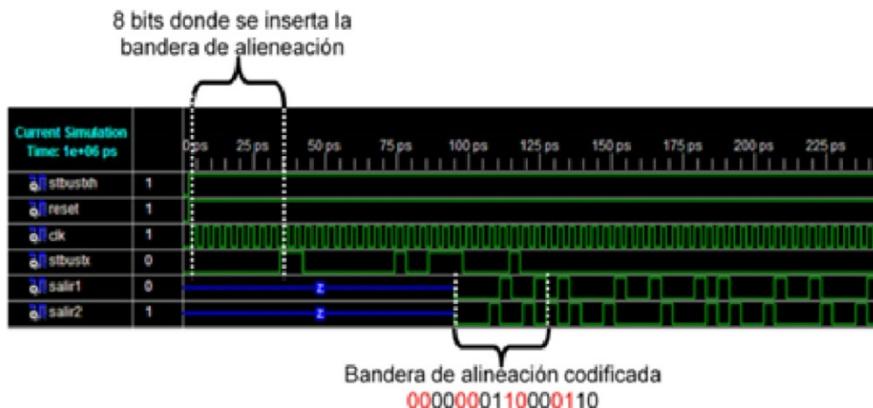

Las señales RESET y STBUSTXH se ponen en ‘1’, lo que equivale a la habilitación del equipo y de la transmisión respectivamente. Estas condiciones establecen que las salidas SALIR1 y SALIR2 deben ofrecer la información entregada por STBUSTX en una trama E1 codificada en HDB3. En la figura 4 se muestra el resultado de la simulación que corrobora el funcionamiento del subsistema.

**Fig. 4.** Simulación del Subsistema Trasmisor.

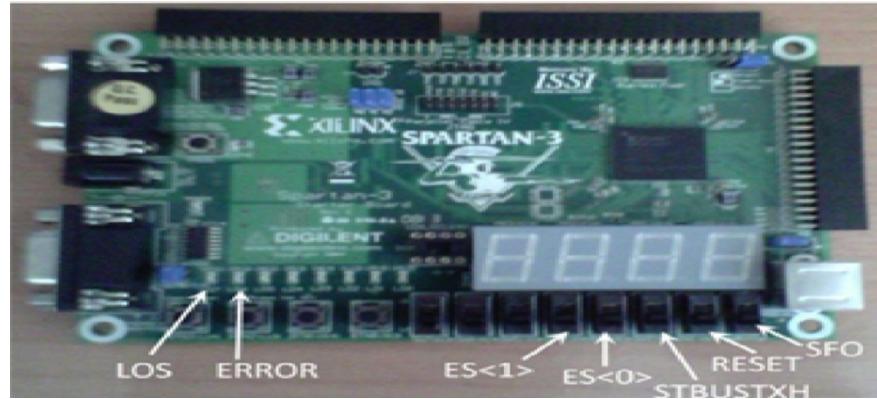

Para la verificación del comportamiento de este sistema en el FPGA, (ver figura 5) se emplearon algunos interruptores de la tarjeta de desarrollo para indicar la inicialización de la transmisión con la activación de la señales: RESET y STBUSTXH. También se cuenta con el interruptor SFO que indica cual pulso de sincronismo será utilizado para marcar el comienzo de cada trama (FT o FO).

**Fig. 5.** Interruptores del sistema transceptor de flujo E1.

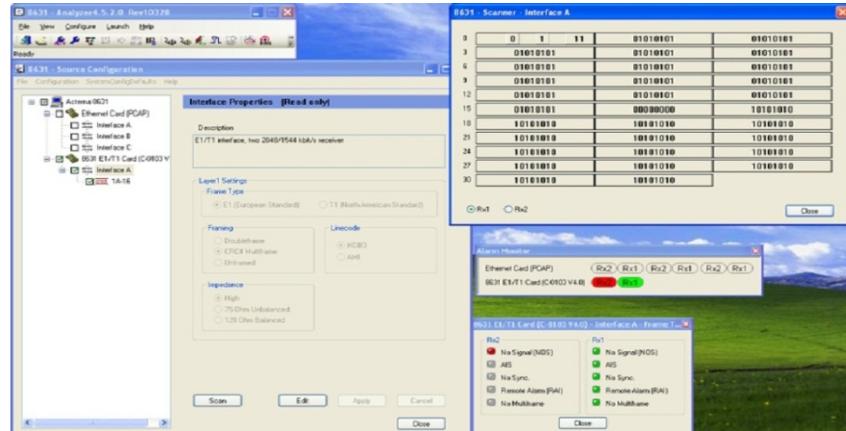

Una vez puestos a ‘1’ los interruptores RESET y STBUSTX, se inicia la captura de los canales de información proporcionados por el STBUSTX, sincronizados con el pulso de sincronismo seleccionado por SFO (FT para esta prueba). A continuación se trasfirieron a los canales por la entrada STBUSTX ‘0’ y ‘1’ alternadamente y se empleó el analizador de protocolos para verificar el funcionamiento a nivel de multitramas como lo muestra la figura 6.

**Fig. 6.** Analizador de protocolo.

El analizador de protocolos permite configurar los parámetros que se desean verificar. En la ventana de configuración fuente (Source configuration) se marca el análisis de la interfaz E1 de 2048 kbps, el comportamiento de la multitrama CRC4 y la codificación HDB3. El monitor de alarmas (Alarm Monitor), no posee ninguna alarma activa en rojo por el canal de recepción al que está conectado el flujo transmitido; por lo que se puede asegurar que el sistema transmisor realiza correctamente la alineación tanto de trama como de multitrama, la comprobación de los errores y la codificación HDB3. Se puede corroborar que a la salida en los canales la información son los ‘1’ y ‘0’ en la ventana que muestra la exploración de

las tramas (Scanner). En el canal cero se muestra la alineación de multitrama CRC y en el canal 16 el mensaje de señalización que en este caso está en cero.

#### 4.2 Comprobación del Receptor

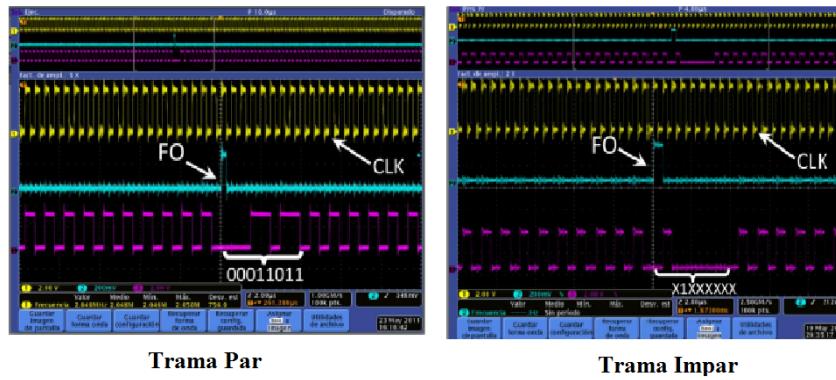

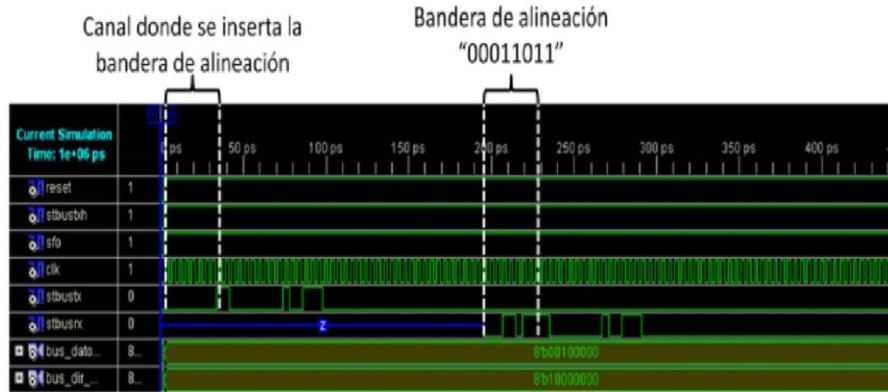

Para la comprobación del subsistema receptor, son de importancia las señales LOS y ERROR porque en dependencia de estas el receptor comienza todo su proceso. Para la comprobación del receptor en el FPGA, se activa el interruptor destinado al RESET para el comienzo de la recepción. Inicialmente el sistema tiene 2 LEDs encendidos (ver figura 5), destinados a las señales LOS y ERROR respectivamente, que constituyen las alarmas del sistema. Cuando la señal obtenida de la decodificación ingresa en el detector de sincronismo, se busca la bandera de alineación de trama. Una vez encontrada y comparados los coeficientes CRC4 recibidos con los calculados en tramas anteriores a la que está siendo detectada, estos leds serán apagados. Para la detección de la alineación en las tramas pares debe encontrarse la bandera: X0011011 y en las tramas impares la secuencia X1XXXXXX como se muestra en la figura 7.

Fig. 7. Canal cero de las tramas pares e impares del bloque receptor.

#### 4.3 Comprobacion de la Interfaz con el Microprocesador

La interfaz con el microprocesador está estrechamente relacionada con los subsistemas de transmisión y recepción; es por ello que para su validación las pruebas están destinadas unas a las memorias que interactúan con el subsistema trasmisor y las otras a las que interactúan con el subsistema receptor.

Con el sistema de transmisión interactúan las memorias: MEMOR1 y MEMORM. La memoria MEMOR1 se utiliza para almacenar las tramas que se forman con los canales proporcionados por el STBUSTX que el procesador desea leer. La memoria MEMORM, se emplea para escribir en el canal (o los canales) que defina el procesador el mensaje (o los mensajes) que quiera insertar en el flujo a transmitir.

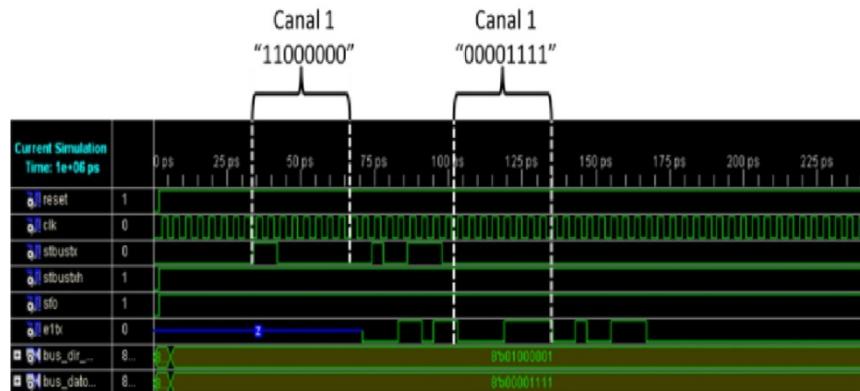

A continuación se presenta la comprobación de la memoria MEMORM. El BUS\_DIR\_M activa la memoria de mensajes del microprocesador con la secuen-

cia “01000001” y además selecciona el canal 1 para la inserción del mensaje. El contenido del mensaje se extrae de BUS\_DATOS\_E\_M, que para esta prueba es ‘00001111’. Como se muestra en la figura 8 la señal STBUSTX presenta otra información en ese canal, mientras que E1TX la sustituye por el mensaje dado por el microprocesador.

**Fig. 8.** Simulación de la interfaz con el microprocesador MEMORM.

Con el sistema receptor interactúan las memorias: MEMOR2 y MEMORM2. La memoria MEMOR2 almacena las tramas que se reciben para que el procesador pueda leerlas. La memoria MEMORM2, almacena la configuración de los modos de habilitación para cada canal del bloque recibido. En la interfaz existe una memoria de propósitos generales que incluyen tanto al sistema transmisor como al receptor. Esta memoria (MEMORM3), se encarga de almacenar los modos de prueba configurados por el microprocesador.

Para comprobar el modo de prueba lazo interno completo se escribe en el BUS\_DIR\_M la secuencia “100XXXXX”, la cual permite seleccionar con los 3 primeros bits, la memoria que almacena los modos de prueba. Luego se le entrega por el BUS\_DATA\_E\_M ‘X01XXXXX’ para indicar con los bits 5 y 6 el modo de prueba a utilizar. Con el fin de restablecer el funcionamiento normal, se vuelve a direccionar la memoria, pero esta vez el procesador debe escribir por el BUS\_DATA\_E\_M la secuencia “X00XXXXX”.

**Fig. 9.** Simulación de la interfaz con el microprocesador MEMORM3.

Como se observa en la figura 9 todos los canales de información que ofrece el STBUSTX inmediatamente después del canal que reserva para la inserción de la bandera de alineación, son los mismos que se reciben por el STBUSRX. Por tanto es posible notar que el sistema se encuentra funcionando en un lazo que conecta su salida transmisora a la entrada de recepción.

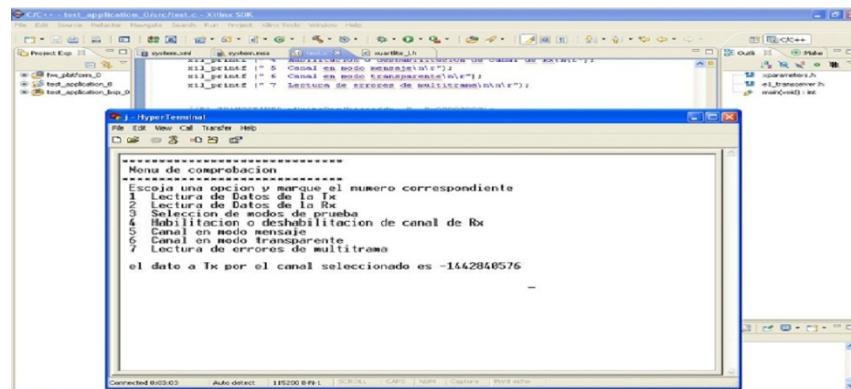

Para validar el grupo de resultados que ofrece la interfaz, se encapsuló todo el sistema tránsceptor en un periférico con un procesador Microblaze. Además se empleó un programa desarrollado en el ambiente SDK con comunicación serie (RS-232) hacia una PC con el fin de efectuar la lectura y escritura de las memorias que conforman la interfaz. En la figura 10 se puede observar el ambiente SDK.

**Fig. 10.** Implementación de la interfaz con el microprocesador MEMOR1.

La primera prueba realizada consistió en la lectura de los datos a transmitir. Para ello se escogió la primera opción del menú y luego se seleccionó el canal 18 para leer. En la figura 10 se observa el valor que devuelve el programa, el cual en hexadecimal es FAA00000H, de este valor para separar el dato del canal, desecharmos el primer simbolo hexadecimal y nos quedamos con los otros dos que

le sigue (AA). El valor entregado por lo tanto es AAH el cual coincide con el valor entregado por el STBUSTX.

A continuación en la figura 11 se muestra la capacidad de habilitar y desahabilitar canales; se deshabilito el canal 13 por lo que en todos va información menos en el 13.

Fig. 11. Implementación de la interfaz con el microprocesador MEMORM2.

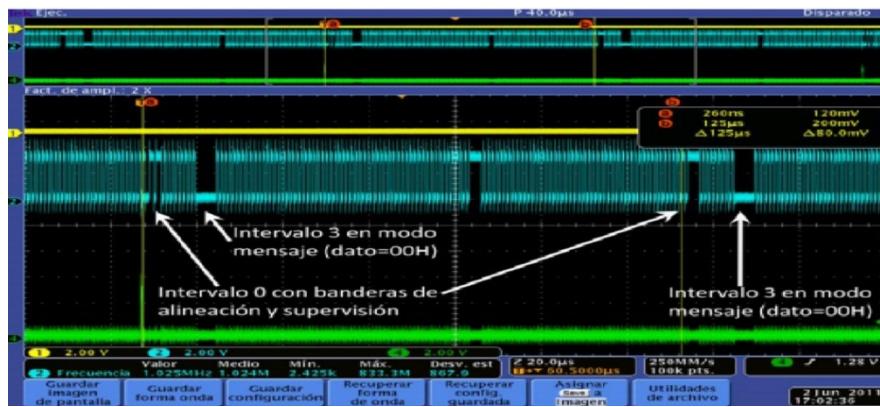

Otra prueba que se realizó fue declarar un canal de los datos a transmitir en modo mensaje.

Fig. 12. Implementación de la interfaz con el microprocesador MEMORM.

En la figura 12 se muestra el siguiente caso. El STBUSTX, el cual contiene en todos sus canales un valor predefinido (55H ó AAH), se le declara en modo mensaje el canal 3 para generar el valor 00H. El canal declarado en modo mensaje se mantendrá con esta configuración hasta que se le indique nuevamente modo transparente.

## **5 Conclusiones**

Mediante la utilización de las herramientas de diseño de Xilinx ISE Design Suite 10.1 y la tarjeta Spartan3 Starter Kit, quedó confeccionado un módulo de propiedad intelectual capaz de transmitir y recibir tramas E1, así como realizar todo el procesamiento necesario para el funcionamiento interno con mejor rendimiento y menor latencia que las soluciones comerciales, con su adecuada sincronización. La interfaz con el microprocesador que tiene incluido es una de las contribuciones de este trabajo, porque brinda un mecanismo de detección de problemas en la transmisión, a través de las pruebas que permite hacer tanto a nivel de trama como a nivel de canal. El análisis de los datos registrados demostró, que tanto en la línea de transmisión como en la de recepción, se llevaron a cabo satisfactoriamente los procesos de alineación de trama y multitrrama, la codificación y decodificación HDB3 y la detección de los errores de la multitrrama mediante el cálculo de los coeficientes CRC4. Además se logró validar el diseño de la interfaz con el microprocesador integrando el sistema con un Microblaze. La verificación de este módulo expuesto en este trabajo permite la creación de un prototipo en desarrollo que integra al transceptor con un microblaze y un controlador hdlc (control de enlace de datos de alto nivel). Ademas, también se puede usar como base para la confección de un módulo de propiedad intelectual T1 (su estándar homologo norte americano) con un esfuerzo mínimo de diseño.

## **6 Referencias**

1. UIT G.732 : Características del equipo múltiplex MIC primario que funciona a 2048 kbit/s.:In: articulo No. E 11161.

2. UIT G.706 : Procedimientos de alineación de trama y de verificación por redundancia cíclica (VRC) relativos a las estructuras de trama básica definidas en la Recomendación G.704.:In:articulo No. E 2101.

3. UIT G.704 : Estructuras de trama síncrona utilizadas en los niveles jerárquicos 1544, 6312, 2048, 8448 y 44736 kbit/s.In:articulo No E 15440.

4. UIT G.703 : Características físicas y eléctricas de los interfaces digitales jerárquicos.:In: articulo No. E 31727.